# PACSystems™ RX3i and RSTi-EP CPU

# **REFERENCE MANUAL**

### Warnings and Caution Notes as Used in this Publication

### **A WARNING**

Warning notices are used in this publication to emphasize that hazardous voltages, currents, temperatures, or other conditions that could cause personal injury exist in this equipment or may be associated with its use.

In situations where inattention could cause either personal injury or damage to equipment, a Warning notice is used.

### **A** CAUTION

Caution notices are used where equipment might be damaged if care is not taken.

**Note:** Notes merely call attention to information that is especially significant to understanding and operating the equipment.

These instructions do not purport to cover all details or variations in equipment, nor to provide for every possible contingency to be met during installation, operation, and maintenance. The information is supplied for informational purposes only, and Emerson makes no warranty as to the accuracy of the information included herein. Changes, modifications, and/or improvements to equipment and specifications are made periodically and these changes may or may not be reflected herein. It is understood that Emerson may make changes, modifications, or improvements to the equipment referenced herein or to the document itself at any time. This document is intended for trained personnel familiar with the Emerson products referenced herein.

Emerson may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not provide any license whatsoever to any of these patents.

Emerson provides the following document and the information included therein as-is and without warranty of any kind, expressed or implied, including but not limited to any implied statutory warranty of merchantability or fitness for particular purpose.

# Contents

| Section     | 1 Introduction                                 | 1              |

|-------------|------------------------------------------------|----------------|

| 1.1         | Revisions in this Manual                       | 2              |

| 1.2         | PACSystems Control System Overview             | 5              |

|             | 1.2.1 Programming and Configuration            | 5              |

|             | 1.2.2 Process Systems                          | 5              |

|             | 1.2.3 PACSystems CPU Models                    | 6              |

| 1.3         | RX3i Overview                                  | 6              |

| 1.4         | RSTi-EP Overview                               | 12             |

| 1.5         | Migrating Series 90 Applications to PACSystems | 13             |

| 1.6         | PACSystems Simulator Overview                  | 14             |

| 1.7         | Documentation                                  | 15             |

|             | 1.7.1 PACSystems Manuals                       | 15             |

|             | 1.7.2 PACEdge Manuals                          | 15             |

|             | 1.7.3 RX3i Manuals                             | 15             |

|             | 1.7.5 RSTi-EP Manuals                          | 16             |

|             | 1.7.6 Series 90 Manuals                        |                |

|             | 1.7.7 Distributed I/O Systems Manuals          | 16             |

|             |                                                |                |

| Section     | 2 CPU Features & Specifications                | 17             |

| Section 2.1 |                                                |                |

|             | Common CPU Features                            | 17             |

|             | Common CPU Features                            | 17<br>17       |

|             | Common CPU Features                            | 17<br>17       |

|             | Common CPU Features                            | 17<br>17<br>17 |

|             | Common CPU Features                            |                |

| 2.1         | Common CPU Features                            |                |

| 2.1         | Common CPU Features                            |                |

|         | 2.2.4 CPU315 and CPU320/CRU320                       | 87           |

|---------|------------------------------------------------------|--------------|

| 2.3     | RSTi-EP CPU Features and Specifications              | 92           |

|         | 2.3.1 CPE100/CPE115                                  |              |

|         | 2.3.2 EPXCPE205, EPXCPE210, EPXCPE215, EPXCPE220, ar | nd EPXCPE240 |

| 0.4     | 105                                                  | 101          |

| 2.4     | · · · · · · · · · · · · · · · · · · ·                |              |

|         | 2.4.1 PACSystems Simulator Operational Notes         | 122          |

| Section | 3 CPU Configuration                                  | 125          |

| 3.1     | Configuring the CPU                                  | 125          |

| 3.2     | Configuration Parameters                             | 126          |

|         | 3.2.1 Settings Parameters                            | 126          |

|         | 3.2.2 Modbus TCP Address Map                         | 129          |

|         | 3.2.3 SNTP                                           | 130          |

|         | 3.2.4 Time                                           | 131          |

|         | 3.2.5 Scan Parameters                                |              |

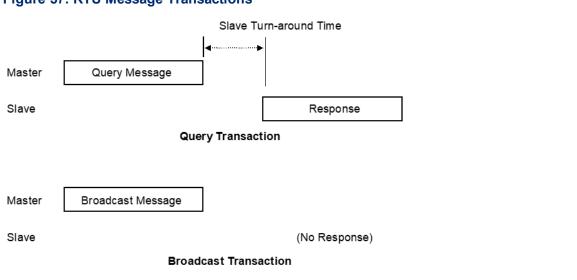

|         | 3.2.6 Memory Parameters                              |              |

|         | 3.2.7 Fault Parameters                               |              |

|         | 3.2.8 Redundancy Parameters (Redundancy CPUs Only)   |              |

|         | 3.2.9 Transfer List                                  |              |

|         | 3.2.10COM1 and COM2 Parameters                       |              |

|         | 3.2.11Scan Sets Parameters                           |              |

|         | 3.2.12Power Consumption Parameters                   |              |

|         | 3.2.13Access Control                                 |              |

|         | 3.2.14OPC UA Parameters                              |              |

| 3.3     | 3,                                                   |              |

| 3.4     | Configuring the Embedded Ethernet Interface          |              |

|         | 3.4.1 Establishing Initial Ethernet Communications   |              |

| 0.5     | 3.4.2 Setting a Temporary IP Address                 |              |

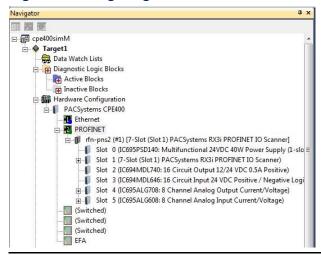

| 3.5     | PACSystems Simulator CPU Configuration               | 152          |

| Section | 4 CPU Operation                                      | 154          |

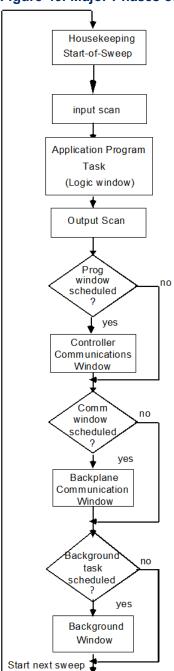

| 4.1     | CPU Sweep                                            | 155          |

|         | 4.1.1 Parts of the CPU Sweep                         | 156          |

|         | 4.1.2 CPU Sweep Modes                                | 158          |

| 4.2     | Program Scheduling Modes                             | 162          |

| 4.3     | Window Modes                                         | 163          |

| 4.4     | Data Coherency in Communications Windows             | 164          |

| 4.5     | Run/Stop Operations.                                 | 164          |

|         | 4.5.1 CPU STOP Modes                                 | 164          |

|         | 4.5.2 STOP to PLIN Mode Transition                   | 168          |

|       |                                               | 4.5.3 RUN Mode Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 169                                                                              |

|-------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|       |                                               | 4.5.4 RUN Mode Store to User Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 171                                                                              |

|       | 4.6                                           | Flash Memory Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 172                                                                              |

|       | 4.7                                           | RUN/STOP Switch Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 174                                                                              |

|       | 4.8                                           | Logic/Configuration Source and CPU Operating Mode at Power-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 174                                                                              |

|       |                                               | 4.8.1 CPU Mode when Memory Not Preserved/Power-up Source is Flash.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 175                                                                              |

|       |                                               | 4.8.2 CPU Mode when Memory Preserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 177                                                                              |

|       | 4.9                                           | Clocks and Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 178                                                                              |

|       |                                               | 4.9.1 Elapsed Time Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 178                                                                              |

|       |                                               | 4.9.2 Time-of-Day Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 178                                                                              |

|       |                                               | 4.9.3 Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 180                                                                              |

|       | 4.10                                          | System Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 181                                                                              |

|       |                                               | 4.10.10EM Protection – Legacy Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 186                                                                              |

|       |                                               | 4.10.2Enhanced Security for Passwords and OEM Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 187                                                                              |

|       |                                               | 4.10.3Legacy/Enhanced Security Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 189                                                                              |

|       | 4.11                                          | PACSystems I/O System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 190                                                                              |

|       |                                               | 4.11.1I/O Configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 190                                                                              |

|       |                                               | 4.11.2I/O System Diagnostic Data Collection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 194                                                                              |

|       |                                               | 4.11.3Power-Up and Power-Down Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 196                                                                              |

|       | 4.12                                          | PACSystems Simulator CPU Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 204                                                                              |

|       |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| Secti | ion 5                                         | 5 Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 204                                                                              |

| Secti | i <b>on 5</b><br>5.1                          | Ethernet Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| Secti |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 204                                                                              |

| Secti |                                               | Ethernet Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 204                                                                              |

| Secti |                                               | Ethernet Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 204<br>205<br>210                                                                |

| Secti | 5.1                                           | Ethernet Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 204<br>205<br>210<br>210                                                         |

| Secti | 5.1                                           | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces  5.1.2 Ethernet Interface Modules.  Serial Communications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 204<br>205<br>210<br>210<br>211                                                  |

| Secti | 5.1                                           | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces.  5.1.2 Ethernet Interface Modules.  Serial Communications.  5.2.1 Serial Port Communications Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                       | 204<br>205<br>210<br>210<br>211<br>214                                           |

| Secti | 5.1                                           | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces.  5.1.2 Ethernet Interface Modules.  Serial Communications.  5.2.1 Serial Port Communications Capabilities  5.2.2 Configurable STOP Mode Protocols                                                                                                                                                                                                                                                                                                                                                                                               | 204<br>205<br>210<br>210<br>211<br>214<br>214                                    |

| Secti | 5.1                                           | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces.  5.1.2 Ethernet Interface Modules.  Serial Communications.  5.2.1 Serial Port Communications Capabilities  5.2.2 Configurable STOP Mode Protocols  5.2.3 Serial Port PIN Assignments.                                                                                                                                                                                                                                                                                                                                                           | 204<br>205<br>210<br>210<br>211<br>214<br>214<br>218                             |

| Secti | 5.1                                           | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces.  5.1.2 Ethernet Interface Modules.  Serial Communications.  5.2.1 Serial Port Communications Capabilities  5.2.2 Configurable STOP Mode Protocols  5.2.3 Serial Port PIN Assignments.  5.2.4 Serial Port Electrical Isolation                                                                                                                                                                                                                                                                                                                   | 204<br>205<br>210<br>210<br>211<br>214<br>214<br>218<br>219                      |

| Secti | 5.1                                           | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces.  5.1.2 Ethernet Interface Modules.  Serial Communications.  5.2.1 Serial Port Communications Capabilities  5.2.2 Configurable STOP Mode Protocols  5.2.3 Serial Port PIN Assignments.  5.2.4 Serial Port Electrical Isolation  5.2.5 Serial Cable Lengths and Shielding                                                                                                                                                                                                                                                                         | 204<br>205<br>210<br>210<br>211<br>214<br>214<br>218<br>219<br>219               |

| Secti | 5.1                                           | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces.  5.1.2 Ethernet Interface Modules.  Serial Communications.  5.2.1 Serial Port Communications Capabilities  5.2.2 Configurable STOP Mode Protocols  5.2.3 Serial Port PIN Assignments.  5.2.4 Serial Port Electrical Isolation  5.2.5 Serial Cable Lengths and Shielding  5.2.6 Maximum Cable Lengths for RSTi-EP CPE205/210/215/220/240.                                                                                                                                                                                                        | 204<br>205<br>210<br>211<br>214<br>214<br>218<br>219<br>219                      |

| Secti | 5.1                                           | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces.  5.1.2 Ethernet Interface Modules.  Serial Communications.  5.2.1 Serial Port Communications Capabilities  5.2.2 Configurable STOP Mode Protocols  5.2.3 Serial Port PIN Assignments.  5.2.4 Serial Port Electrical Isolation.  5.2.5 Serial Cable Lengths and Shielding.  5.2.6 Maximum Cable Lengths for RSTi-EP CPE205/210/215/220/240.  5.2.7 Serial Port Baud Rates                                                                                                                                                                        | 204<br>205<br>210<br>211<br>214<br>214<br>218<br>219<br>220<br>221               |

| Secti | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces.  5.1.2 Ethernet Interface Modules.  Serial Communications.  5.2.1 Serial Port Communications Capabilities  5.2.2 Configurable STOP Mode Protocols  5.2.3 Serial Port PIN Assignments.  5.2.4 Serial Port Electrical Isolation.  5.2.5 Serial Cable Lengths and Shielding  5.2.6 Maximum Cable Lengths for RSTi-EP CPE205/210/215/220/240.  5.2.7 Serial Port Baud Rates  5.2.9 Programmable Coprocessor Module (PCM).  PACSystems Simulator Communications                                                                                      | 204<br>205<br>210<br>211<br>214<br>218<br>219<br>220<br>221<br>222               |

|       | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces  5.1.2 Ethernet Interface Modules  Serial Communications  5.2.1 Serial Port Communications Capabilities  5.2.2 Configurable STOP Mode Protocols  5.2.3 Serial Port PIN Assignments  5.2.4 Serial Port Electrical Isolation  5.2.5 Serial Cable Lengths and Shielding  5.2.6 Maximum Cable Lengths for RSTi-EP CPE205/210/215/220/240  5.2.7 Serial Port Baud Rates  5.2.9 Programmable Coprocessor Module (PCM)  PACSystems Simulator Communications                                                                                             | 204<br>205<br>210<br>211<br>214<br>218<br>219<br>220<br>221<br>222               |

|       | 5.1<br>5.2<br>5.3                             | Ethernet Communications  5.1.1 Embedded Ethernet Interfaces.  5.1.2 Ethernet Interface Modules.  Serial Communications.  5.2.1 Serial Port Communications Capabilities  5.2.2 Configurable STOP Mode Protocols  5.2.3 Serial Port PIN Assignments.  5.2.4 Serial Port Electrical Isolation.  5.2.5 Serial Cable Lengths and Shielding.  5.2.6 Maximum Cable Lengths for RSTi-EP CPE205/210/215/220/240.  5.2.7 Serial Port Baud Rates.  5.2.9 Programmable Coprocessor Module (PCM).  PACSystems Simulator Communications.                                                                                   | 204<br>205<br>210<br>211<br>214<br>214<br>218<br>219<br>220<br>221<br>222<br>223 |

|       | 5.1<br>5.2<br>5.3                             | Ethernet Communications.  5.1.1 Embedded Ethernet Interfaces. 5.1.2 Ethernet Interface Modules. Serial Communications.  5.2.1 Serial Port Communications Capabilities 5.2.2 Configurable STOP Mode Protocols. 5.2.3 Serial Port PIN Assignments. 5.2.4 Serial Port Electrical Isolation. 5.2.5 Serial Cable Lengths and Shielding. 5.2.6 Maximum Cable Lengths for RSTi-EP CPE205/210/215/220/240. 5.2.7 Serial Port Baud Rates. 5.2.9 Programmable Coprocessor Module (PCM). PACSystems Simulator Communications.  Serial I/O, SNP & RTU Protocols.  Configuring Serial Ports Using COMMREQ Function 65520. | 204<br>205<br>210<br>211<br>214<br>218<br>219<br>220<br>221<br>222<br>223<br>224 |

|     | 6.1.4 Invalid Port Configuration Combinations                                   | 224  |

|-----|---------------------------------------------------------------------------------|------|

|     | 6.1.5 COMMREQ Command Block Parameter Values                                    | 224  |

|     | 6.1.7 Example COMMREQ Data Block for Configuring Message mode Protocol          | 226  |

|     | 6.1.8 Example COMMREQ Command Blocks for Serial Port Setup function             | n226 |

|     | 6.1.9 Example COMMREQ Command Block for Configuring SNP Protocol                | 227  |

|     | 6.1.10Example COMMREQ Data Block for Configuring RTU Protocol                   | 228  |

|     | 6.1.11Example COMMREQ Data Block for Configuring Serial I/O Protocol.           | 229  |

| 6.2 | Serial I/O Proto col.                                                           | 230  |

|     | 6.2.1 Calling Serial I/O COMMREQs from the CPU Sweep                            | 230  |

|     | 6.2.2 Compatibility                                                             | 230  |

|     | 6.2.3 Status Word for Serial I/O COMMREQs                                       | 231  |

|     | 6.2.4 Serial I/O COMMREQ Commands                                               | 233  |

|     | 6.2.5 Overlapping COMMREQs                                                      | 233  |

|     | 6.2.6 Initialize Port Function (4300)                                           | 234  |

|     | 6.2.7 Set Up Input Buffer Function (4301)                                       | 235  |

|     | 6.2.8 Flush Input Buffer Function (4302)                                        | 235  |

|     | 6.2.9 Read Port Status Function (4303)                                          | 236  |

| 6.3 | For reference, see the tables under in 4.12 PACSystems Simulator CPU Operation. | 237  |

|     | 6.3.2 Write Port Control Function (4304)                                        | 239  |

|     | 6.3.3 Cancel COMMREQ Function (4399)                                            | 240  |

|     | 6.3.4 Autodial Function (4400)                                                  | 241  |

|     | 6.3.5 Write Bytes Function (4401)                                               | 243  |

|     | 6.3.6 Read Bytes Function (4402)                                                | 243  |

|     | 6.3.7 Read String Function (4403)                                               | 245  |

| 6.4 | RTU Slave Protocol                                                              | 247  |

|     | 6.4.1 Message Format                                                            | 248  |

|     | 6.4.2 Cyclic Redundancy Check (CRC)                                             | 253  |

|     | 6.4.3 RTU Message Descriptions                                                  | 259  |

|     | 6.4.4 RTU Scratch Pad                                                           | 275  |

|     | 6.4.5 Communication Errors                                                      | 276  |

|     | 6.4.6 RTU Slave/SNP Slave Operation with Programmer Attached                    | 279  |

| 6.5 | SNP Slave Protocol                                                              | 280  |

|     | 6.5.1 Permanent Datagrams                                                       | 280  |

|     | 6.5.2 Communication Requests (COMMREQs) for SNP                                 | 280  |

| 6.6 | PACSystems Simulator Serial I/O, SNP, & RTU Protocols                           | 281  |

|     | Appendix A: Performance Data                                                    | 282  |

| A-1 | Boolean Execution Measurements (ms per 1000 Boolean executions)                 | 282  |

| A-2 | Instruction Timing                                                              |      |

| A-3 | RX3i & RSTi-EP Instruction Times                                                | 285  |

| A-5  | Overhead Sweep Impact Times                                                                                               | 286 |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

| A-6  | Base Sweep Times                                                                                                          | 287 |

| A-7  | Base Sweep vs. Full Sweep Phases                                                                                          | 288 |

| A-8  | What the Sweep Impact Tables Contain                                                                                      | 289 |

| A-9  | Programmer Sweep Impact Times                                                                                             | 290 |

| A-10 | I/O Scan and I/O Fault Sweep Impact                                                                                       | 291 |

| A-11 | Sweep Impact of Local I/O Modules                                                                                         | 291 |

| A-12 | RX3i I/O Module Types                                                                                                     | 292 |

| A-13 | RX3i I/O Module Sweep Impact Times                                                                                        | 293 |

| A-14 | Worksheet A: I/O Module Sweep Time                                                                                        | 294 |

| A-15 | Sweep Impact of Genius I/O and GBCs                                                                                       | 295 |

| A-16 | Sweep Impact Time of Genius I/O and GBCs                                                                                  | 296 |

| A-17 | Worksheet B: Genius I/O Sweep Time                                                                                        | 297 |

| A-18 | Ethernet Global Data Sweep Impact                                                                                         | 298 |

| A-19 | Exchange Overhead                                                                                                         | 298 |

| A-20 | Data Transfer Time                                                                                                        | 300 |

| A-21 | Worksheet C: Ethernet Global Data Sweep Time                                                                              | 302 |

| A-22 | EGD Sweep Impact for RX3i CPE330 and CPE400/CPL410/CPS400                                                                 | 302 |

| A-23 | EGD Sweep Impact for RX3i CPE302/CPE305/CPE310 and RSTi-EP CPE100/CPE115 Embedded Ethernet Interface                      | 303 |

| A-25 | Example Calculation for EGD Utilization on RX3i CPE302/CPE305/CPl and RSTi-EP CPE100/CPE115                               |     |

| A-26 | Normal Sweep – EGD on RX3i CPE302/CPE305/CPE310, RSTi-EP CF Series, and RSTi-EP CPE100/CPE115 Embedded Ethernet Interface |     |

| A-27 | Constant Sweep - EGD on RX3i CPE302/CPE305/CPE310 and RSTi-ECPE100/CPE115 Embedded Ethernet Interface                     |     |

| A-28 | Sweep Impact of Intelligent Option Modules                                                                                | 308 |

| A-29 | Fixed Sweep Impact Times of RX3i Intelligent Option Modules                                                               | 309 |

| A-30 | PROFINET Controller (PNC001) and PROFINET I/O Sweep Impact                                                                | 310 |

| A-31 | DSM314 Sweep Impact                                                                                                       | 312 |

| A-32 | I/O Interrupt Performance and Sweep Impact                                                                                | 312 |

| A-33 | I/O Interrupt Block Performance and Sweep Impact Times                                                                    | 313 |

| A-34 | Dropped Interrupts                                                                                                        | 314 |

| A-35 | Worksheet D: Programmer, IOM, I/O Interrupt Sweep Time                                                                    | 315 |

| A-36 | Timed Interrupt Performance                                                                                               | 316 |

|      | Appendix B: User Memory Allocation                                                                                        | 317 |

| B-1  | Items that Count Against User Memory                                                                                      | 318 |

| B-2  | User Program Memory Usage                                                                                                 |     |

| B-3  | %L and %P Program Memory                                                                                                  |     |

| B-4  | Program Logic and Overhead                                                                                                | 319 |

Contents vi

Contents

# **Table of Figures**

| Figure 1: Configuring an Embedded PROFINET Controller                         | 21           |

|-------------------------------------------------------------------------------|--------------|

| Figure 2: Example ipconfigml                                                  | 32           |

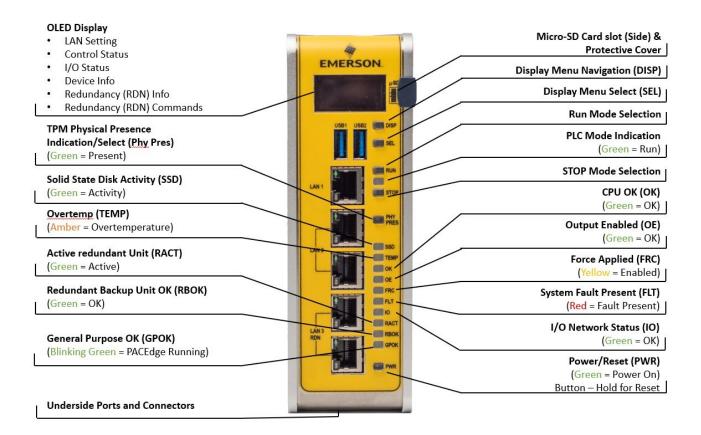

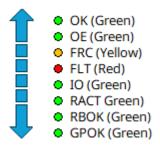

| Figure 3: CPE400/CPL410/ Front View and Features                              | 44           |

| Figure 4: CPS400 Front View and Features                                      | 45           |

| Figure 5: Underside Ports & Connectors                                        | 54           |

| Figure 6: CPE400 Micro-SD & USB Connectors                                    | 57           |

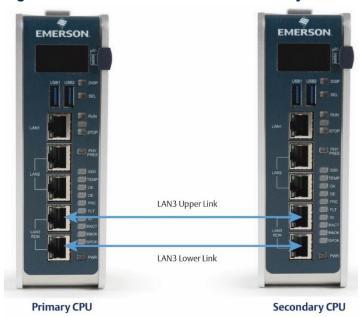

| Figure 7:Location of RTC Battery on CPE400/CPL410/CPS400                      | 58           |

| Figure 8: LAN3 Interconnects for Hot Standby Redundancy                       | 60           |

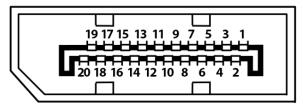

| Figure 9: Display Port Connector                                              | 62           |

| Figure 10: Front Display Port                                                 | 64           |

| Figure 11: CPE330 Run/Stop Switch and RDSD Switches                           | 66           |

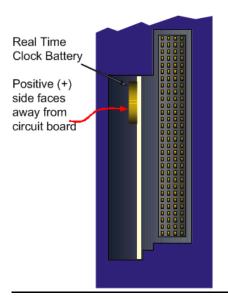

| Figure 12: Location and Orientation of Real-Time Clock Battery in CPE330      | 69           |

| Figure 13: IC695CPE302/CPE305-Axxx Front View                                 | 73           |

| Figure 14: IC695CPE310 Front View                                             | 73           |

| Figure 15: CPE302/305/310-Bxxx                                                |              |

| Figure 16: External Features of CPE302/CPE305-Axxx                            | 76           |

| Figure 17: External Features of CPE310-Axxx/Bxxx                              | 76           |

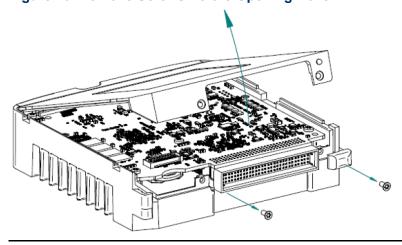

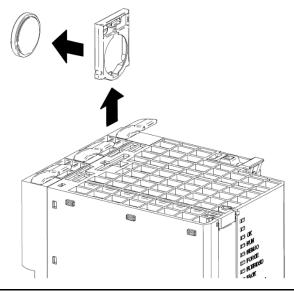

| Figure 18: Accessing Real-Time Clock Battery (CPE302-Axxx, CPE305-Axxx, and C | PE310-Axxx80 |

| Figure 19: Sample Tool for Battery Removal                                    | 82           |

| Figure 20: Remove Screws Before Opening Cover                                 | 82           |

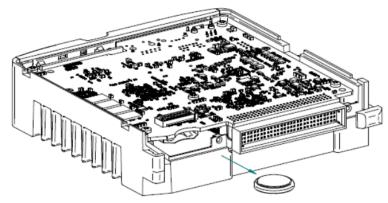

| Figure 21: Use Tweezers to Remove Battery                                     | 83           |

| Figure 22: Remove Battery from the Retaining Clip of the Rear of the Module   | 84           |

| Figure 23: IC695CPU320 Front View                                             | 87           |

| Figure 24: CPU310 Front View                                                  | 90           |

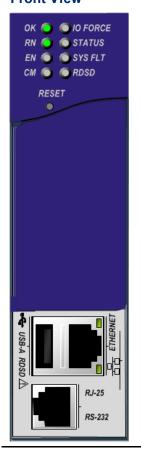

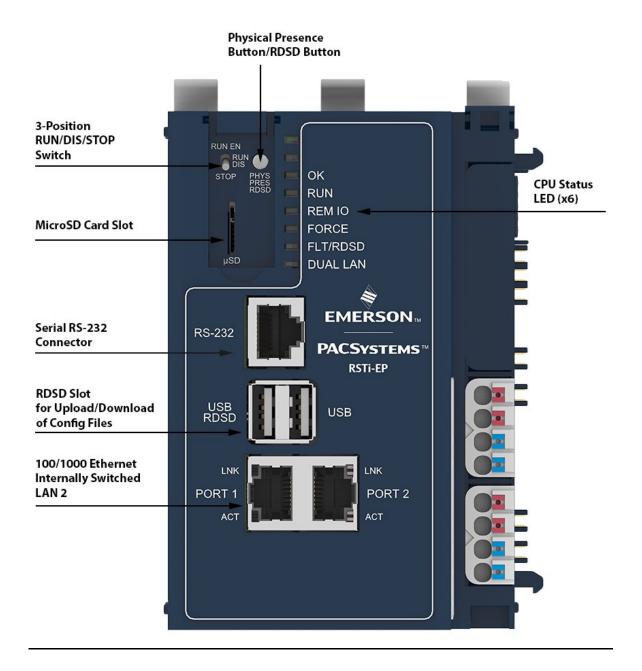

| Figure 25: CPE100 Front, Top, and Bottom Views and Features                   | 97           |

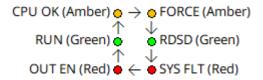

| Figure 26: CPE100/CPE115 Membrane Pushbutton and Module Status LEDs           | 100          |

| Figure 27: State Diagram for CPE100/CPE115 Run/Stop Operation                 | 100          |

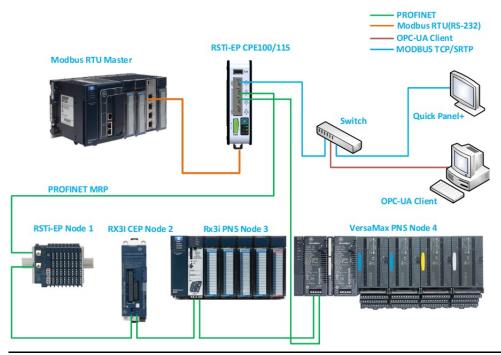

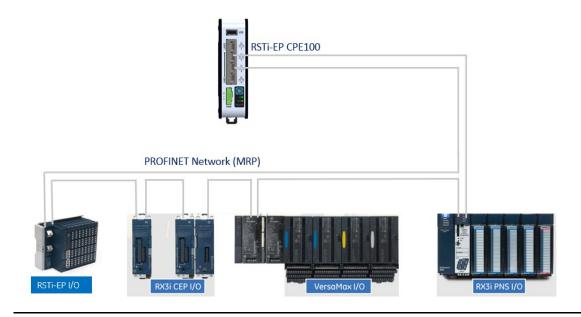

| Figure 28: Typical Multi-Tier LAN Application (Star/Bus Topology)             | 103          |

| Figure 29: Typical Multi-Tier LAN Application (Ring Topology)                 | 103          |

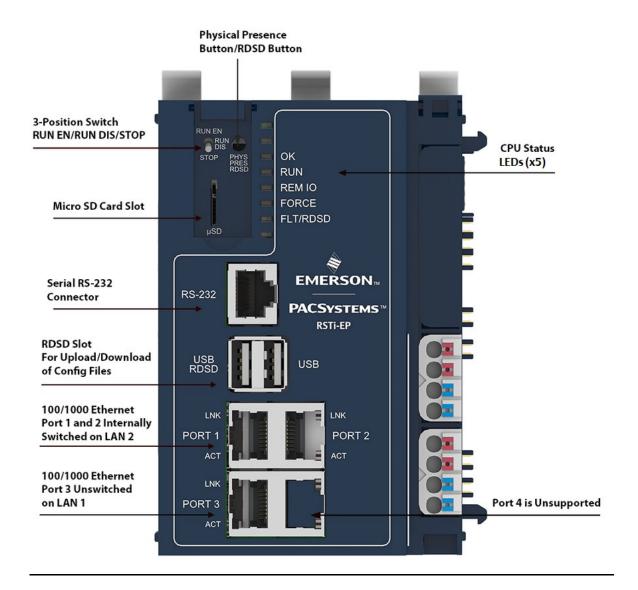

| Figure 30: EPXCPE205                                                          |              |

| Figure 31: EPXCPE210/215/220/240                                              | 108          |

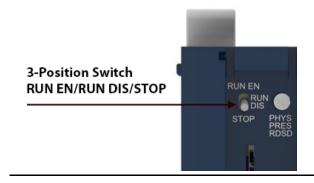

| Figure 32: 3-Position Switch RUN ENRUN DIS/STOP                               | 110          |

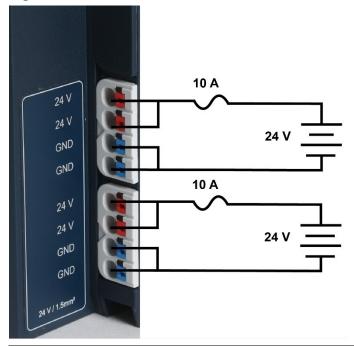

| Figure 33: Power Feed Minimum Current Draw                                    | 114          |

| Figure 34: Power Feed Maximum Current Draw                                    | 114          |

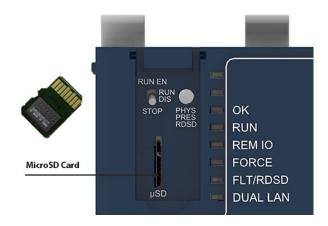

| Figure 35: MicroSD                                                            | 115          |

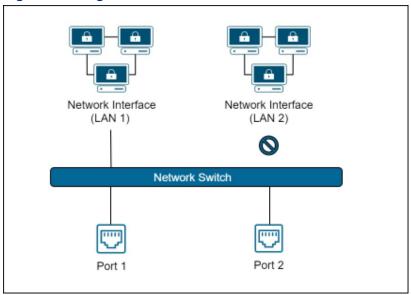

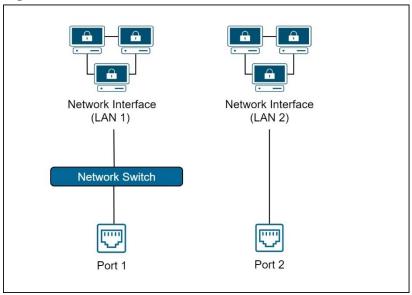

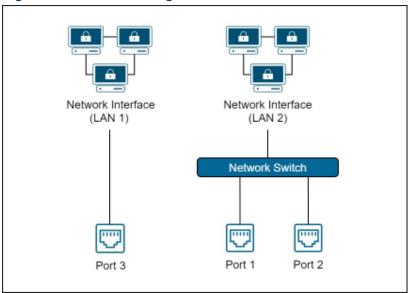

| Figure 36: Single-LAN Mode                                                    | 116          |

| Figure 37: Dual-LAN Mode                                                      |              |

| Figure 38: Network Configuration                                              | 117          |

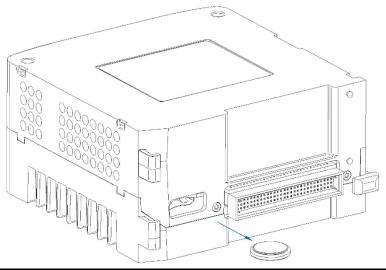

| Figure 39: CPE2XX Battery Replacement                                         |              |

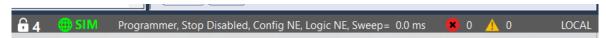

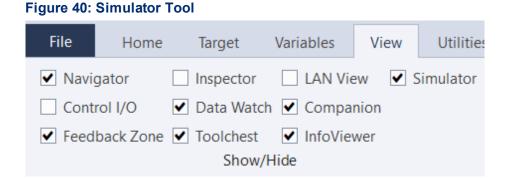

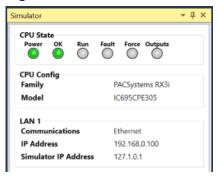

| Figure 40: Simulator Tool                                                     | 122          |

| Figure 41: Simulator Window                                                   | 123          |

| Figure 42: Hidden Items                                                       |              |

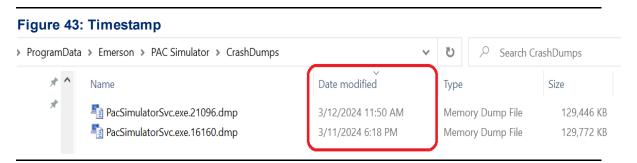

| Figure 43: Timestamp                                                          | 124          |

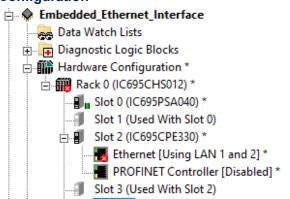

| Figure 44: Embedded Ethernet Interface Configuration                          | 146          |

| Figure 45: Set Temporary IP Address                                  | 151 |

|----------------------------------------------------------------------|-----|

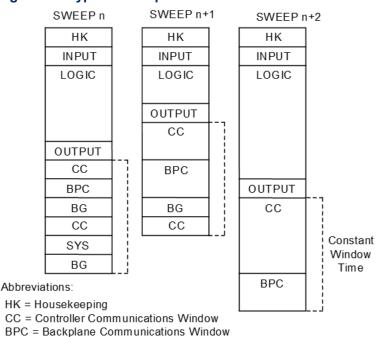

| Figure 46: Major Phases of a Typical CPU Sweep                       | 156 |

| Figure 47: Typical Sweeps in Normal Sweep Mode                       | 159 |

| Figure 48: Typical Sweeps in Constant Sweep Mode                     | 161 |

| Figure 49: Typical Sweeps in Constant Window Mode                    | 162 |

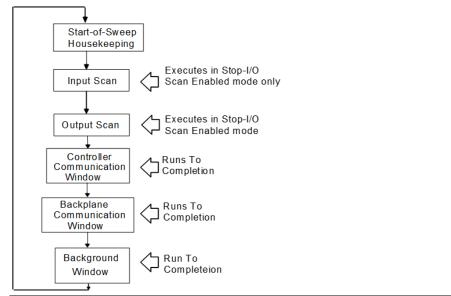

| Figure 50: CPU Sweep in Stop-I/O Disabled and Stop-I/O Enabled Modes | 165 |

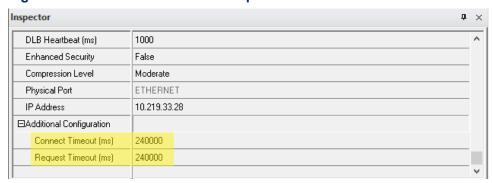

| Figure 51: Connect Timeout and Request Timeout                       | 172 |

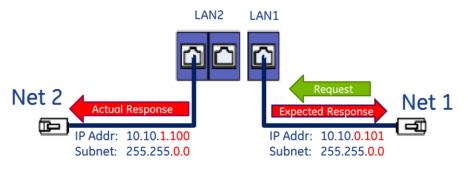

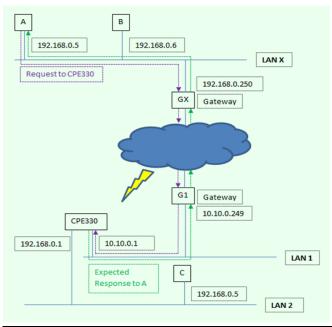

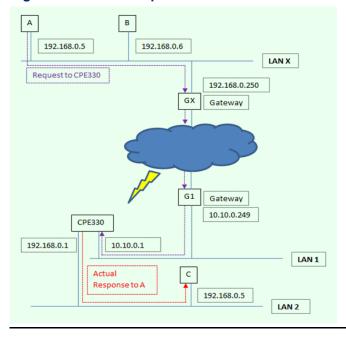

| Figure 52: CPE330 Overlapping Local IP Subnet Example                | 206 |

| Figure 53: Expected Response Path                                    | 208 |

| Figure 54: Actual Response Path                                      | 208 |

| Figure 55: COM1 Port CPE400/CPL410/CPS400                            | 217 |

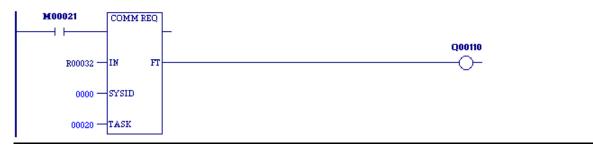

| Figure 56: COMMREQ Example                                           | 224 |

| Figure 57: RTU Message Transactions                                  | 248 |

| Figure 58: Message Fields in a Frame                                 | 249 |

| Figure 59: RTU Read Output Table Example                             | 251 |

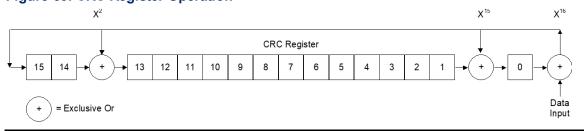

| Figure 60: CRC Register Operation                                    | 254 |

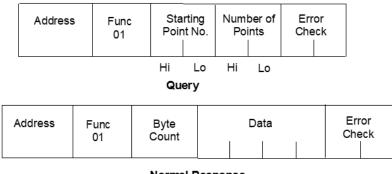

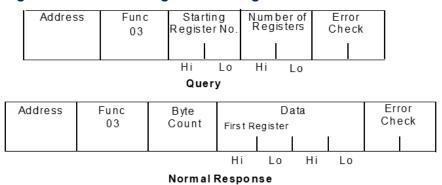

| Figure 61: RTU Read Output Table Message Format                      | 259 |

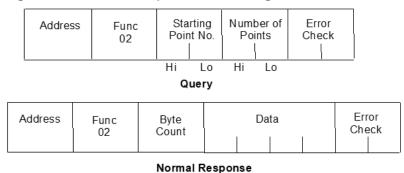

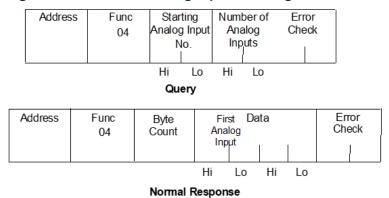

| Figure 62: RTU Read Input Table Message Format                       | 260 |

| Figure 63: RTU Read Registers Message Format                         | 261 |

| Figure 64: RTU Read Analog Inputs Message Format                     | 262 |

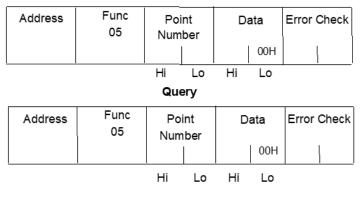

| Figure 65: RTU Force Single Output Message Format                    | 264 |

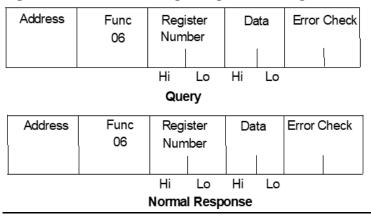

| Figure 66: RTU Preset Single Register Message Format                 | 265 |

| Figure 67: RTU Read Exception Status Message Format                  | 266 |

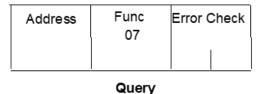

| Figure 68: RTU Loopback/Maintenance Message Format                   | 267 |

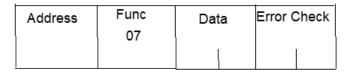

| Figure 69: RTU Force Multiple Outputs Message Format                 | 269 |

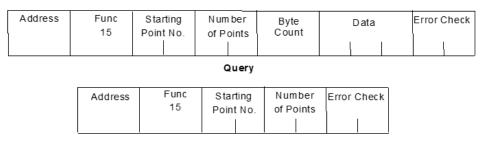

| Figure 70: RTU Preset Multiple Registers Message Format              | 270 |

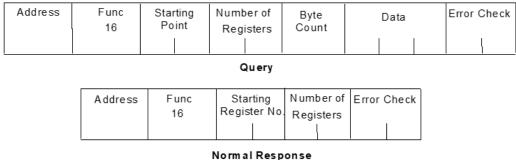

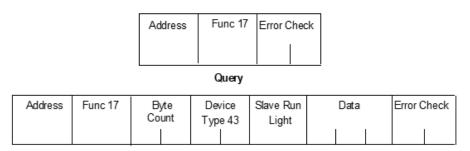

| Figure 71: RTU Report Device Type Message Format                     | 270 |

| Figure 72: RTU Read Scratch Pad Memory Message Format                | 275 |

| Figure 73: Error Response to Query Format                            | 277 |

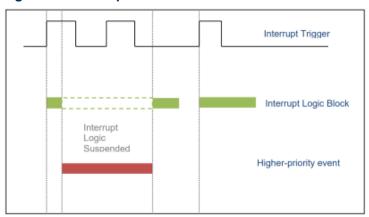

| Figure 74: Interrupt Execution Considerations                        | 314 |

# Section 1 Introduction

This manual contains general information about PACSystems CPU operation and product features.

Section 1 provides a **general introduction** to the PACSystems family of products, including new features, product overviews, and a list of related documentation.

Section 2 provides CPU Features & Specifications.

**Installation procedures** for the different platforms are described in their respective manuals as given below:

- PACSystems RX7i Installation Manual, GFK-2223.

- PACSystems RX3i System Manual, GFK-2314.

- RSTi-EP User Manual, GFK-2958.

CPU Programming is covered in *PACSystems RX3i* and *RSTi-EP CPU Programmer's Reference Manual*, GFK-2950. It provides an overview of program structure and describes the various languages which may be used, their syntax and operation, and provides examples.

Section 3 describes the CPU Configuration. Configuration using the proprietary PAC Machine Edition™ (PME) programming and configuration software package determines the characteristics of CPU, System, and module operation. It also establishes the program references used by each module in the system. For details on the configuration of RX3i Ethernet Interface modules, refer to PACSystems RX3i and RSTi-EP TCP/IP Ethernet Communications User Manual, GFK-2224.

# 1.1 Revisions in this Manual

**Note:** A given feature may not be implemented on all PACSystems CPUs. To determine whether a feature is available on a given CPU model and firmware version, please refer to the Important Product Information (IPI) document provided for the CPU version that you are using.

| Rev | Date       | Description                                                                 |

|-----|------------|-----------------------------------------------------------------------------|

| AY  | Dec 2024   | Updated Document to support PACSystems Simulator                            |

|     | 2 00 202 1 | Updated Section 3.2.1 and 4.5.4 to include CPE400/CPL410 for RMS to User    |

|     |            | Flash.                                                                      |

| AX  | May 2023   | Added mentions of CPE400/CPL410 to Section 4.8 with SVC_REQ 63              |

|     |            | information.                                                                |

|     |            | Updated Section 3.2.1 to include new RMS to User Flash Settings             |

|     |            | parameter.                                                                  |

| AW  | Feb 2023   | Updated Section 4.5.4 to include CPE330 for RMS to User Flash.              |

|     |            | Changed Section 4.6.1 to Section 4.7.                                       |

|     |            | Updated Section 4.8 with SVC_REQ 63 information.                            |

|     |            | Updates to support CPE200 Series controllers                                |

|     |            | Updates to support CPE310-Bxxx controller                                   |

| AV  | Nov 2022   | Updates to support OPC UA 2D Array Access                                   |

|     |            | Updates to support firmware release 10.70                                   |

|     |            | Updates to sections 4.10.1 and 4.10.3 to address the new Legacy             |

|     |            | Client/Server Protocol Memory Access feature and other Password and         |

|     |            | Privilege Level enhancements.                                               |

|     |            | Updates to support the release of CPE302/305-Bxxx.                          |

| AU  | Jul- 2022  | Added note about RMS to flash performance in Section 3.2.13                 |

| AU  | Jui- 2022  | Addition of RSTi-EP EPXCPE200 series controllers.                           |

|     |            | Updates to Access Control List                                              |

|     |            | Updates to Flash Memory and Override Tables                                 |

|     |            | Correction to the maximum number of supported simplex & redundant           |

|     |            | PROFINET devices.                                                           |

| AT  | Sep-2021   | Updates to CPE400/CPL410 in support of PACEdge Software updates.            |

| AQ  | May-2021   | Updates regarding the number of supported PROFINET devices for the          |

| 710 | Way-2021   | CPL410.                                                                     |

| AP  | Nov-2020   | Revised instructions for the STOP-Halt auto-recovery feature for the latest |

|     |            | firmware release 10.05 in the section entitled STOP Halt Mode               |

| AN  | Jun-2020   | Updated discussion of STOP-Halt mode recovery to include new auto-          |

|     |            | recovery functionality in sections 4.5.1.3 and 4.8.3.                       |

|     | May-2020   | Updated CPE/CPL Features and Specifications in Section 2.2                  |

| AM  |            | Updated Tables 4-3 and 4-4 in Section Privilege Level Request from PAC      |

|     | F 1 0000   | Machine Edition                                                             |

| AL  | Feb-2020   | Addition of DNP3 to CPE400                                                  |

|     |            | Updated to reflect updated capabilities of FW 9.90                          |

| AK  | Oct-2019   | Following Emerson's acquisition of this product, changes have been made to  |

|     |            | apply appropriate branding and registration of the product with required    |

|     | 1 6040     | certification agencies.                                                     |

| AJ  | Jun-2019   | Updated Appendix A on Boolean Execution for clarity.                        |

| Rev      | Date      | Description                                                                                                                      |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------|

| . 10 7   | 20.00     | CPE400/CPL410 added the ability to recover from STOP-Halt mode.                                                                  |

|          |           | CPE330 supports HSB CPU redundancy with Single RMX. This support                                                                 |

| AH       | Apr-2019  | includes CRU320 compatible mode. Dual RMX configuration is no longer a                                                           |

|          |           | requirement.1                                                                                                                    |

|          |           | CPE330/CPE400/CPL410 increased block count from 512 to 768 including                                                             |

| AG       | Nov-2018  | Main                                                                                                                             |

| <u> </u> | 1         | SoE and other minor changes for CPE330                                                                                           |

| AF       | Aug-2018  | European DST correction                                                                                                          |

|          | 1.1.0040  | Addition of IC695CPL410, CPU .                                                                                                   |

| AE       | Jul-2018  | Addition of IC695PNS101.                                                                                                         |

| AD       | Apr-2018  | Added CPE115 module                                                                                                              |

|          |           | Updated throughout for addition of CPE302 (initial firmware version 9.40).                                                       |

| 100      | Feb-2018  | CPE400 Serial IO feature added                                                                                                   |

| AC       | Feb-2018  | New Authorized Firmware Update feature noted (part of RX3i firmware                                                              |

|          |           | version 9.40).                                                                                                                   |

|          |           | Added Redundancy features for CPE400                                                                                             |

| AB       | Oct-2017  | Updated Field Agent information for CPE400.                                                                                      |

| Ab       | OCI-2017  | Updated Section 2.2 for new features of CPE400.                                                                                  |

|          |           | Added Section 2.1.11 on CPU Over-Temperature behavior.                                                                           |

| AA       | Sep-2017  | Addition of support for Media Redundancy Protocol (MRP) on CPE100.                                                               |

|          |           | Addition of RSTi-EP EPSCPE100 (new product) and updated other relevant                                                           |

|          |           | sections.                                                                                                                        |

| Z        | May-2017  | Addition of Simple Network Time Protocol (SNTP), Coordinated Universal                                                           |

|          |           | Time (UTC), and Daylight Savings Time (DST) features for CPE305, CPE310,                                                         |

|          |           | CPE330, and CPE400.                                                                                                              |

|          |           | Added section on CPE400 and incorporated into CPU comparison table                                                               |

|          |           | (section 2.2). This section also introduces Field Agent and documents how to set up Embedded Field Agent for the CPE400 (section |

| Υ        | Dec-2016  | Added section 2.1.6, Embedded PROFINET Controller.                                                                               |

|          |           | Update of Energy Pack to include ACC403 and compatibility matrix.                                                                |

|          |           | Added compatibility mode information for CPE330 with CPU320 & CRU320                                                             |

| X        | Feb-2016  | Corrected Ethernet Indicators CPE305 & CPE310 table.                                                                             |

| W        | Aug-2015  | Addition of support for Ethernet Global Data (Class 1) on CPE330                                                                 |

|          | <u> </u>  | Addition of RX3i CPE330 (new product) and related Ethernet considerations.                                                       |

|          |           | Update of Energy Pack to include ACC402 and compatibility matrix.                                                                |

|          |           | Addition of HART® Pass-Through feature (see page 9).                                                                             |

| .,       | lum 2045  | Addition of CPU Comparison Charts                                                                                                |

| V        | Jun-2015  | Update of Communications Section (4.12). Removed original Sections 5-11                                                          |

|          |           | (Sections dealing with CPU programming) and Section 14 (Diagnostics).                                                            |

|          |           | These are now in PACSystems RX3i CPU Programmer's Reference Manual,                                                              |

|          |           | GFK-2950 (Sections 2-8 and Section 9 respectively).                                                                              |

| U        | Nov-2014  | New section for EGD Sweep Impact for RX3i CPE302/CPE305/CPE310 and                                                               |

| "        | 1107-2014 | RSTi-EP CPE100/CPE115 Embedded Ethernet Interface.                                                                               |

<sup>&</sup>lt;sup>1</sup> Requires PME 9.50 SIM 14 or later and CPE330 firmware 9.75 or later.

| Rev     | Date      | Description                                                                                              |

|---------|-----------|----------------------------------------------------------------------------------------------------------|

|         |           | Support for OPC UA using embedded Ethernet port in CPE305/CPE310 with                                    |

|         |           | CPU firmware 8.20.                                                                                       |

|         |           | Support for Ethernet Global Data (EGD Class 1) using embedded Ethernet                                   |

|         |           | port in CPE305/CPE310 with CPU firmware 8.30 Sweep impact of EGD on                                      |

| Т       | Oct-2014  | Embedded Ethernet interface. Direct replacement for S90-30 IC693CPU374.                                  |

|         |           | New communications capabilities are provided by:                                                         |

|         |           | IC695PNS001 – PROFINET Scanner Module                                                                    |

|         |           | IC695GCG001 – Genius Communications Gateway via PROFINET                                                 |

|         |           | IC695EDS001 – Ethernet-based DNP3 Outstation                                                             |

|         |           | Support for Modbus/TCP Server, SRTP channels, and Modbus/TCP client                                      |

|         |           | channels on RX3i CPE305/CPE310 embedded Ethernet interface – Section                                     |

|         |           | 2 & 4.12                                                                                                 |

|         |           | Support for Access Control List – Section 3                                                              |

|         |           | Modbus TCP/IP mapping for CPE305/CPE310 – Section 3 Enhanced Security Passwords and OEM Protection – 3.5 |

|         |           | Serial I/O protocol enhancements (Data Set Ready, Ring Indicator, and Data                               |

| s       | July-2013 | Carrier Detect) – 5.3                                                                                    |

|         |           | Diagnostics for PROFINET alarms and PROFINET network faults, including                                   |

|         |           | #PNIO_ALARM, SA0030 – refer to PACSystems RX7i and RX3i CPU                                              |

|         |           | Programmer's Reference Manual, GFK-2950 Section 3 & Section 9.                                           |

|         |           | Instruction executions times measured for RX3i CPU320/CRU320 – 6.6                                       |

|         |           | Sweep impact times for new modules: IC694MDL758, IC694APU300-CA and                                      |

|         |           | later, IC695PNS001, IC694ALG442, IC694ALG220, IC694MDL645, and                                           |

|         |           | IC694MDL740-6.6                                                                                          |

|         |           | Added instructions for replacing the RX3i CPE305/CPE310 real-time clock                                  |

|         |           | battery: Section 2.                                                                                      |

|         |           | Corrected definitions of reverse acting and direct-acting modes for PID                                  |

|         |           | functions: refer to PACSystems RX7i and RX3i CPU Programmer's                                            |

|         |           | Reference Manual, GFK-2950 Section 7.                                                                    |

| earlier |           | Expanded data for Boolean execution measurements – 6.6                                                   |

|         |           | Re-instated instruction times for RX7i CPE030/CRE030/CPE040 release 6.0                                  |

|         |           | as published in version Q of the manual (unintentionally omitted from version R) $-6.6$                  |

|         |           | Compatibility information for volatile memory backup batteries has been                                  |

|         |           | consolidated in the PACSystems Battery and Energy Pack Manual, GFK-                                      |

|         |           | 2741 – throughout                                                                                        |

# 1.2 PACSystems Control System Overview

The PACSystems controller environment combines performance, productivity, openness, and flexibility. The PACSystems control system integrates advanced technology with existing systems. The result is seamless migration that protects your investment in I/O and application development.

## 1.2.1 Programming and Configuration

PAC Machine Edition programming software provides a universal engineering development environment for all programming, configuration, and diagnostics of PACSystems. A PACSystems CPU is programmed and configured using the programming software to perform process and discrete automation for various applications. The CPU communicates with I/O and smart option modules through a rack-mounted backplane. It communicates with the programmer and/or HMI devices via the Ethernet ports or the serial ports COM1 and COM2 using Serial I/O, or Modbus RTU slave protocols.

## 1.2.2 Process Systems

PACSystems CPUs with firmware version 5.0 and later support PAC Process Systems (PPS). PPS is a complete, tightly integrated, seamless process control system using PACSystems, HMI/SCADA, and PAC Production Management Software to provide control, optimization, and performance management to manage and monitor batch or continuous manufacturing. It delivers the tools required to design, implement, document, and maintain an automated process. For information about purchasing PPS software, refer to the Support website.

## 1.2.3 PACSystems CPU Models

| Family                                                   | Catalog #                                 | Description                                                                                                    |

|----------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                                          | EPXCPE205                                 | 512 KB user memory                                                                                             |

|                                                          | EPXCPE210                                 | 1 MB user memory                                                                                               |

| RSTi-EP CPUs                                             | EPXCPE215                                 | 1.5 MB user memory                                                                                             |

|                                                          | EPXCPE220                                 | 2 MB user memory                                                                                               |

|                                                          | EPXCPE240                                 | 4 MB user memory                                                                                               |

| RSTi-EP Standalone CPUs                                  | EPSCPE100                                 | 1 MB user memory                                                                                               |

| RSTI-EF Standardie CFUS                                  | EPSCPE115                                 | 1.5 MB user memory                                                                                             |

| RX3i Standalone CPUs with                                | IC695CPE400                               | 64 MB user memory with                                                                                         |

| embedded                                                 | 10093CFE400                               | PACEdge + Connext                                                                                              |

| Ethernet/PROFINET Interface                              | IC695CPL410                               | 64 MB user memory with                                                                                         |

| ElliellievFROFINET illiellace                            | 10093CFL410                               | PACEdge + WebHMI                                                                                               |

| RX3i Standalone Safety                                   | IC695CPS400                               | 64 MB user memory for SIL-2                                                                                    |

| Controller                                               | 1009301 3400                              | Safety System                                                                                                  |

| RX3i CPUs with embedded<br>Ethernet/PROFINET Interface   | IC695CPE330                               | 64 MB user memory                                                                                              |

| DV3: CDU a with analysis of                              | IC695CPE302                               | 2 MB user memory <sup>3</sup>                                                                                  |

| RX3i CPUs with embedded  Ethernet Interface <sup>2</sup> | IC695CPE305                               | 6 MB user memory <sup>4</sup>                                                                                  |

| Emernet interface-                                       | IC695CPE310                               | 13 MB user memory <sup>5</sup>                                                                                 |

|                                                          | IC695CPU310                               | 10 MB user memory                                                                                              |

|                                                          | IC695CPU315                               | 20 MB user memory                                                                                              |

|                                                          | IC695CPU320                               | 64 MB user memory                                                                                              |

| RX3i CPUs                                                | IC695NIU001+<br>versions –AAAA &<br>later | For information, refer to the<br>PACSystems RX3i Ethernet<br>Network Interface Unit User's<br>Manual, GFK-2439 |

|                                                          | IC695NIU001                               | For information, refer to the<br>PACSystems RX3i Ethernet<br>Network Interface Unit User's<br>Manual, GFK-2439 |

| RX3i Redundancy CPU                                      | IC695CRU320                               | 64 MB user memory                                                                                              |

### 1.3 RX3i Overview

The RX3i control system hardware consists of an RX3i universal backplane and up to seven Series 90-30 expansion or remote racks. The CPU can be in any slot in the universal backplane except the last slot, which is reserved for the serial bus transmitter, IC695LRE001.

The RX3i supports user-defined Function Blocks (LD logic only) and Structured Text programming.

6